SystemRDL語(yǔ)法、IC驗(yàn)證資料與專業(yè)社區(qū)全解析

在集成電路(IC)設(shè)計(jì),特別是復(fù)雜片上系統(tǒng)(SoC)的開(kāi)發(fā)流程中,寄存器抽象層的高效描述與功能驗(yàn)證是確保芯片成功的關(guān)鍵環(huán)節(jié)。本文將圍繞SystemRDL規(guī)范示例、IC驗(yàn)證技術(shù)資料以及相關(guān)的專業(yè)工程師社區(qū),為微電子與電子電路領(lǐng)域的從業(yè)者提供一個(gè)綜合性的知識(shí)導(dǎo)航。

一、SystemRDL:寄存器描述的標(biāo)準(zhǔn)化語(yǔ)言

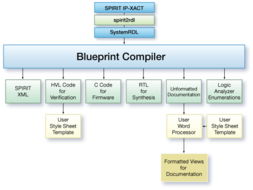

SystemRDL(System Register Description Language)是一種專門用于描述數(shù)字系統(tǒng)中寄存器和內(nèi)存映射的硬件描述語(yǔ)言。它超越了傳統(tǒng)的IP-XACT或自定義表格,提供了一種機(jī)器可讀且功能豐富的標(biāo)準(zhǔn)方式。

語(yǔ)法示例與核心概念:

一個(gè)簡(jiǎn)單的SystemRDL定義可能如下所示:`systemrdl

addrmap top {

reg myreg {

field {} data @0x0;

};

};`

此例定義了一個(gè)名為“top”的地址映射,其中包含一個(gè)寄存器“myreg”,該寄存器在偏移地址0x0處有一個(gè)名為“data”的字段。SystemRDL的強(qiáng)大之處在于其能精確定義字段的訪問(wèn)權(quán)限(如讀/寫、只讀)、硬件行為(如寫后清除、計(jì)數(shù)器)、復(fù)位值以及復(fù)雜的層次化地址空間結(jié)構(gòu)。掌握其語(yǔ)法對(duì)于生成精確的寄存器傳輸級(jí)(RTL)代碼、驗(yàn)證測(cè)試平臺(tái)、C/C++頭文件以及文檔至關(guān)重要。

二、IC驗(yàn)證:確保設(shè)計(jì)正確的基石

IC驗(yàn)證是使用仿真、形式驗(yàn)證、硬件仿真等多種方法,確保RTL設(shè)計(jì)符合功能規(guī)格和性能要求的過(guò)程。相關(guān)技術(shù)資料涵蓋極廣:

- 方法論與語(yǔ)言:以通用驗(yàn)證方法學(xué)(UVM)為主導(dǎo),結(jié)合SystemVerilog語(yǔ)言,構(gòu)建標(biāo)準(zhǔn)化、可重用的驗(yàn)證平臺(tái)。資料包括UVM框架詳解、測(cè)試用例(Testbench)構(gòu)建、序列(Sequence)、驅(qū)動(dòng)器(Driver)、監(jiān)視器(Monitor)和記分板(Scoreboard)的設(shè)計(jì)。

- 驗(yàn)證IP(VIP):針對(duì)標(biāo)準(zhǔn)接口(如AMBA AXI、USB、PCIe)的預(yù)驗(yàn)證組件,能極大加速驗(yàn)證進(jìn)程。學(xué)習(xí)如何集成和使用VIP是重要課題。

- 模擬與調(diào)試:涉及主流仿真工具(如Synopsys VCS, Cadence Xcelium, Siemens EDA Questa)的使用技巧、覆蓋率(代碼覆蓋率、功能覆蓋率)收集與分析、以及高效的調(diào)試技術(shù)。

- 前沿技術(shù):形式驗(yàn)證、便攜式激勵(lì)(PSS)、硬件輔助驗(yàn)證(如FPGA原型驗(yàn)證、硬件仿真器)的相關(guān)資料也日益重要。

三、專業(yè)工程師社區(qū)與論壇:知識(shí)分享與問(wèn)題求解的沃土

電子工程師的成長(zhǎng)離不開(kāi)同行交流。以下社區(qū)是獲取資料、探討難題的寶貴平臺(tái):

- EETOP(創(chuàng)芯網(wǎng)論壇):國(guó)內(nèi)最具影響力的集成電路專業(yè)社區(qū)之一。其板塊全面覆蓋IC設(shè)計(jì)、IC驗(yàn)證、嵌入式設(shè)計(jì)、微電子、半導(dǎo)體制造與工藝、電子電路、EDA工具等。論壇內(nèi)活躍著大量資深工程師和學(xué)生,分享大量實(shí)用資料、面試經(jīng)驗(yàn)、工具腳本和項(xiàng)目討論,是初學(xué)者入門和從業(yè)者深造的必訪之地。

- 電子工程師論壇:一個(gè)更廣義的電子技術(shù)交流平臺(tái),不僅限于IC,還廣泛涉及電子電路設(shè)計(jì)、單片機(jī)、電源技術(shù)、嵌入式設(shè)計(jì)、測(cè)試測(cè)量等。對(duì)于解決板級(jí)系統(tǒng)集成、模擬電路問(wèn)題以及嵌入式軟件開(kāi)發(fā)非常有幫助。

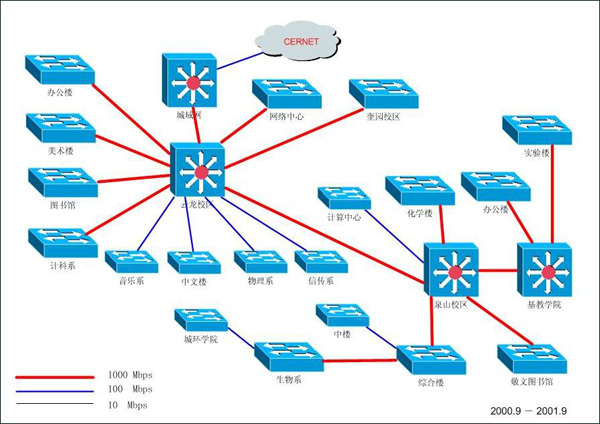

- 網(wǎng)絡(luò)工程設(shè)計(jì)相關(guān)社區(qū):雖然與核心IC設(shè)計(jì)有一定距離,但在涉及網(wǎng)絡(luò)處理器、通信芯片、高速SerDes等設(shè)計(jì)時(shí),網(wǎng)絡(luò)協(xié)議和系統(tǒng)架構(gòu)知識(shí)不可或缺。相關(guān)論壇有助于拓寬系統(tǒng)視野。

###

從精確描述寄存器行為的SystemRDL語(yǔ)法,到構(gòu)建復(fù)雜驗(yàn)證環(huán)境的UVM和SystemVerilog知識(shí),再到從EETOP等專業(yè)論壇獲取實(shí)戰(zhàn)經(jīng)驗(yàn)和最新資訊,構(gòu)成了IC設(shè)計(jì)與驗(yàn)證工程師的核心能力圖譜。持續(xù)學(xué)習(xí)、積極在社區(qū)中參與討論與分享,是在快速發(fā)展的半導(dǎo)體行業(yè)中保持競(jìng)爭(zhēng)力的有效途徑。建議工程師們系統(tǒng)性地學(xué)習(xí)標(biāo)準(zhǔn)語(yǔ)法與驗(yàn)證方法學(xué),同時(shí)善用論壇資源,將理論知識(shí)與工程實(shí)踐緊密結(jié)合,從而在集成電路的創(chuàng)新浪潮中創(chuàng)造價(jià)值。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.kingofman.cn/product/26.html

更新時(shí)間:2026-04-15 07:40:10